Product Summary

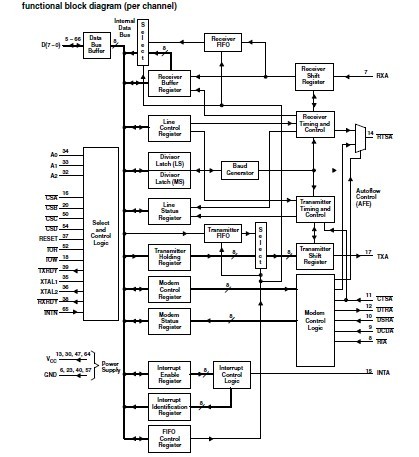

The TL16C554AIPNR is an enhanced quadruple version of the TL16C550C asynchronous-communications element (ACE). Each channel performs serial-to-parallel conversion on data characters received from peripheral devices or modems and parallel-to-serial conversion on data characters transmitted by the CPU. The complete status of each channel of the quadruple ACE can be read by the CPU at any time during operation. The information obtained includes the type and condition of the operation performed and any error conditions encountered. The TL16C554AIPNR quadruple ACE can be placed in an alternate FIFO mode, which activates the internal FIFOs to allow 16 bytes (plus three bits of error data per byte in the receiver FIFO) to be stored in both receive and transmit modes. In the FIFO mode of operation, there is a selectable autoflow control feature that can significantly reduce software overhead and increase system efficiency by automatically controlling serial-data flow using RTS output and CTS input signals. All logic is on the chip to minimize system overhead and maximize system efficiency. Two terminal functions of the TL16C554AIPNR allow signaling of direct-memory access (DMA) transfers.

Parametrics

TL16C554AIPNR absolute maximum ratings: (1)Supply voltage range, VCC: –0.5 V to 7 V; (2)Input voltage range at any input, VI: –0.5 V to 7 V; (3)Output voltage range, VO: –0.5 V to VCC + 3 V; (4)Continuous total-power dissipation at (or below) 70℃: 500 mW; (5)Operating free-air temperature range, TA: TL16C554A: 0℃ to 70℃; (6)TL16C554AI: –40℃ to 85℃; (7)Storage temperature range, Tstg: –65℃ to 150℃.

Features

TL16C554AIPNR features: (1)Integrated Asynchronous-Communications Element; (2)Consists of Four Improved TL16C550C ACEs Plus Steering Logic; (3)In FIFO Mode, Each ACE Transmitter and Receiver Is Buffered With 16-Byte FIFO to Reduce the Number of Interrupts to CPU; (4)In TL16C450 Mode, Hold and Shift Registers Eliminate Need for Precise Synchronization Between the CPU and Serial Data; (5)Up to 16-MHz Clock Rate for up to 1-Mbaud Operation; (6)Programmable Baud-Rate Generators Which Allow Division of Any Input Reference Clock by 1 to (216–1) and Generate an Internal 16 × Clock; (7)Adds or Deletes Standard Asynchronous Communication Bits (Start, Stop, and Parity) to or From the Serial-Data Stream; (8)Independently Controlled Transmit, Receive, Line Status, and Data Set Interrupts; (9)5-V and 3.3-V Operation.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

TL16C554AIPNR |

Texas Instruments |

UART Interface IC Quad UART with 16-Byte FIFOs |

Data Sheet |

|

|

||||||||||

|

TL16C554AIPNRG4 |

Texas Instruments |

UART Interface IC Quad UART with 16-Byte FIFOs |

Data Sheet |

|

|

||||||||||

(China (Mainland))

(China (Mainland))