Product Summary

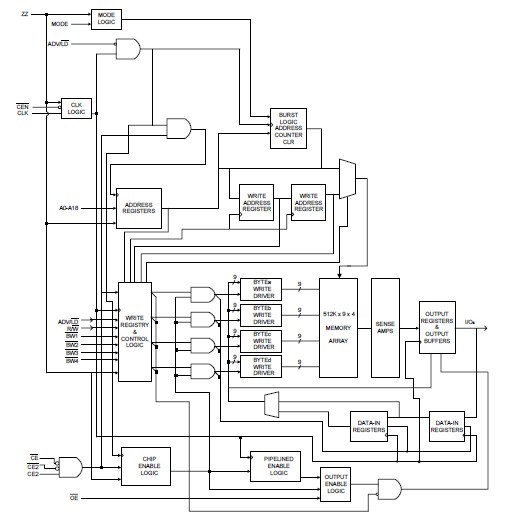

The a67l0300-0133b AMIC Zero Bus Latency (ZeBLTM) SRAM employs high-speed, low-power CMOS designs using an advanced CMOS process. The a67l0300-0133b SRAM integrate a 1M X 18, 512K X 36 SRAM core with advanced synchronous peripheral circuitry and a 2-bit burst counter. These a67l0300-0133b is optimized for 100 percent bus utilization without the insertion of any wait cycles during Write-Read alternation. The positive edge triggered single clock input (CLK) controls all synchronous inputs passing through the registers.

Parametrics

a67l0300-0133b absolute maximum ratings: (1)Power Supply Voltage (VCC): -0.3V to +4.6V; (2)Voltage Relative to GND for any Pin Except VCC (Vin, Vout): -0.3V to VCC +0.3V; (3)Operating Temperature (Topr): 0°C to 70°C; (4)Storage Temperature (Tbias): -10°C to 85 °C; (5)Storage Temperature (Tstg): -55°C to 125°C; (6)ICC Power Supply Current : Operating: 460 mA.

Features

a67l0300-0133b features: (1)Zero Bus Latency between READ and WRITE cycles allows 100% bus utilization; (2)Signal +3.3V ± 5% power supply; (3)Individual Byte Write control capability; (4)Clock enable (CEN)pin to enable clock and suspend operations; (5)Clock-controlled and registered address, data and control signals; (6)Registered output for pipelined applications; (7)Three separate chip enables allow wide range of options for CE control, address pipelining; (8)Internally self-timed write cycle; (9)Selectable BURST mode (Linear or Interleaved); (10)SLEEP mode (ZZ pin)provided; (11)Available in 100 pin LQFP package.

Diagrams

(China (Mainland))

(China (Mainland))